# C6.1 About the A64 base instructions

*Alphabetical list of A64 base instructions* gives full descriptions of the A64 instructions that are in the following instruction groups:

- Branch, Exception generation, and System instructions.

- Loads and stores associated with the general-purpose registers.

- Data processing (immediate).

- Data processing (register).

*A64 instruction set encoding* provides an overview of the instruction encodings as well as of the instruction classes within their functional groups.

The rest of this section is general description of the base instructions. It contains the following subsections:

- Register size.

- Use of the PC.

- Use of the stack pointer.

- Condition flags and related instructions.

## C6.1.1 Register size

Most data processing, comparison, and conversion instructions that use the general-purpose registers as the source or destination operand have two instruction variants that operate on either a 32-bit or a 64-bit value.

Where a 32-bit instruction form is selected, the following holds:

- The upper 32 bits of the source registers are ignored.

- The upper 32 bits of the destination register are set to zero.

- Right shifts and right rotates inject at bit[31], not at bit[63].

- The Condition flags, where set by the instruction, are computed from the lower 32 bits.

This distinction applies even when the results of a 32-bit instruction form are indistinguishable from the lower 32 bits computed by the equivalent 64-bit instruction form. For example, a 32-bit bitwise ORR could be performed using a 64-bit ORR and simply ignoring the top 32 bits of the result. However, the A64 instruction set includes separate 32-bit and 64-bit forms of the ORR instruction.

As well as distinct sign-extend or zero-extend instructions, the A64 instruction set also provides the ability to extend and shift the final source register of an ADD, SUB, ADDS, or SUBS instruction and the index register of a load/store instruction. This enables array index calculations involving a 64-bit array pointer and a 32-bit array index to be implemented efficiently.

The assembly language notation enables the distinct identification of registers holding 32-bit values and registers holding 64-bit values. See *Register names* and *Register indexed addressing*.

## C6.1.2 Use of the PC

A64 instructions have limited access to the PC. The only instructions that can read the PC are those that generate a PC relative address:

- ADR and ADRP.

- The Load register (literal) instruction class.

- Direct branches that use an immediate offset.

- The unconditional branch with link instructions, BL and BLR, that use the PC to create the return link address.

Only explicit control flow instructions can modify the PC:

- Conditional and unconditional branch and return instructions.

- Exception generation and exception return instructions.

For more details of instructions that can modify the PC, see *Branches, Exception generating, and System instructions*.

## C6.1.3 Use of the stack pointer

A64 instructions can use the stack pointer only in a limited number of cases:

- Load/store instructions use the current stack pointer as the base address:

- When stack alignment checking is enabled by system software and the base register is SP, the current stack pointer must be initially quadword aligned, That is, it must be aligned to 16 bytes. Misalignment generates an SP alignment fault. See SP alignment checking for more information.

- Add and subtract data processing instructions in their immediate and extended register forms, use the current stack pointer as a source register or the destination register or both.

- Logical data processing instructions in their immediate form use the current stack pointer as the destination register.

### C6.1.4 Condition flags and related instructions

The A64 base instructions that use the Condition flags as an input are:

- Conditional branch. The conditional branch instruction is B. cond.

- Add or subtract with carry. These instruction types include instructions to perform multi-precision arithmetic and calculate checksums. The add or subtract with carry instructions are ADC, ADCS, SBC, and SBCS, or an architectural alias for these instructions.

- Conditional select with increment, negate, or invert. This instruction type conditionally selects between one source register and a second, incremented, negated, inverted, or unmodified source register. The conditional select with increment, negate, or invert instructions are CSINC, CSINV, and CSNEG.

These instructions also implement:

- Conditional select or move. The Condition flags select one of two source registers as the destination register. Short conditional sequences can be replaced by unconditional instructions followed by a conditional select, CSEL.

- Conditional set. Conditionally selects between 0 and 1, or 0 and -1. This can be used to convert the Condition flags to a Boolean value or mask in a general-purpose register, for example. These instructions include CSET and CSETM.

- Conditional compare. This instruction type sets the Condition flags to the result of a comparison if the original condition is true, otherwise it sets the Condition flags to an immediate value. It permits the flattening of nested conditional expressions without using conditional branches or performing Boolean arithmetic within the general-purpose registers. The conditional compare instructions are CCMP and CCMN.

The A64 base instructions that update the Condition flags as an output are:

- Flag-setting data processing instructions, such as ADCS, ADDS, ANDS, BICS, RMIF, SBCS, SETF8, SETF16, and SUBS, and the aliases CMN, CMP, and TST.

- Conditional compare instructions such as CCMN, CCMP.

- The random number generation instructions MRS RNDR and MRS RNDRRS, see *Effect of random number generation instructions on Condition flags*.

The A64 base instructions that manipulate the Condition flags are:

• The flag manipulation instruction CFINV, which inverts the value of the Carry flag.

If FEAT\_FlagM2 is implemented, the base instructions AXFLAG and XAFLAG. These instructions convert between the Arm floating point comparison PSTATE condition flag format and an alternative format shown in Table C6-1.

### Table C6-1 Relationship between ARM format and alternative format PSTATE condition flags

|              | AR | M fo | orma | t | Alternative format |   |   |   |  |  |  |  |

|--------------|----|------|------|---|--------------------|---|---|---|--|--|--|--|

| Result       | Ν  | Ζ    | С    | V | Ν                  | Ζ | С | V |  |  |  |  |

| Greater than | 0  | 0    | 1    | 0 | 0                  | 0 | 1 | 0 |  |  |  |  |

| Less than    | 1  | 0    | 0    | 0 | 0                  | 0 | 0 | 0 |  |  |  |  |

| Equal        | 0  | 1    | 1    | 0 | 0                  | 1 | 1 | 0 |  |  |  |  |

| Unordered    | 0  | 0    | 1    | 1 | 0                  | 1 | 0 | 0 |  |  |  |  |

The flags can be directly accessed for a read/write using the NZCV, Condition Flags.

The A64 base instructions also include conditional branch instructions that do not use the Condition flags as an input:

- Compare and branch if a register is zero or nonzero, CBZ and CBNZ.

- Test a single bit in a register and branch if the bit is zero or nonzero, TBZ and TBNZ.

## Effect of random number generation instructions on Condition flags

If FEAT\_RNG is implemented, then:

- When a valid random number is returned, the PSTATE.NZCV flags are set to 0b0000.

- If the random number hardware is not capable of returning a random number in a reasonable period of time, the PSTATE.NZCV flags are set to 0b0100, and the random number generation instructions return the value 0.

— Note -

The definition of "reasonable period of time" is IMPLEMENTATION DEFINED. The expectation is that software might use this as an opportunity to reschedule or run a different routine, perhaps after a small number of retries have failed to return a valid value.

# C6.2 Alphabetical list of A64 base instructions

This section lists every instruction in the base category of the A64 instruction set. For details of the format used, see *Understanding the A64 instruction descriptions*.

## C6.2.1 ABS

Absolute value computes the absolute value of the signed integer value in the source register, and writes the result to the destination register.

### Integer

(FEAT\_CSSC)

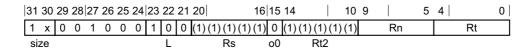

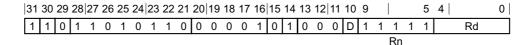

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 |    | 5 | 4 |    | 0 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|----|---|---|----|---|

| sf | 1  | 0  | 1  | 1  | 0  | 1  | 0  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  |   | Rn |   |   | Rd |   |

## 32-bit variant

Applies when sf == 0.

ABS <Wd>, <Wn>

### 64-bit variant

Applies when sf == 1.

ABS <Xd>, <Xn>

### Decode for all variants of this encoding

```

if !IsFeatureImplemented(FEAT_CSSC) then UNDEFINED;

constant integer datasize = 32 << UInt(sf);

integer n = UInt(Rn);

integer d = UInt(Rd);

```

## Assembler symbols

| <wd></wd> | Is the 32-bit name of the general-purpose destination register, encoded in the "Rd" field. |

|-----------|--------------------------------------------------------------------------------------------|

| <wn></wn> | Is the 32-bit name of the general-purpose source register, encoded in the "Rn" field.      |

| <xd></xd> | Is the 64-bit name of the general-purpose destination register, encoded in the "Rd" field. |

| <xn></xn> | Is the 64-bit name of the general-purpose source register, encoded in the "Rn" field.      |

## Operation

```

bits(datasize) operand1 = X[n, datasize];

integer result = Abs(SInt(operand1));

X[d, datasize] = result<datasize-1:0>;

```

## **Operational information**

If PSTATE.DIT is 1:

•

- The execution time of this instruction is independent of:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

- The response of this instruction to asynchronous exceptions does not vary based on:

- The values of the data supplied in any of its registers.

— The values of the NZCV flags.

## C6.2.2 ADC

Add with Carry adds two register values and the Carry flag value, and writes the result to the destination register.

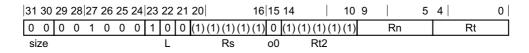

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 |    | 5 | 4  | 0 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|----|---|----|---|

| sf | 0  | 0  | 1  | 1  | 0  | 1  | 0  | 0  | 0  | 0  | Rm |    | 0  | 0  | 0  | 0  | 0  | 0  |   | Rn |   | Rd |   |

|    | ор | S  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |    |   |    |   |

#### 32-bit variant

Applies when sf == 0.

ADC <Wd>, <Wn>, <Wm>

#### 64-bit variant

Applies when sf == 1.

ADC <Xd>, <Xn>, <Xm>

#### Decode for all variants of this encoding

integer d = UInt(Rd); integer n = UInt(Rn); integer m = UInt(Rm); constant integer datasize = 32 << UInt(sf);</pre>

#### **Assembler symbols**

| <wd></wd> | Is the 32-bit name of the general-purpose destination register, encoded in the "Rd" field.   |

|-----------|----------------------------------------------------------------------------------------------|

| <wn></wn> | Is the 32-bit name of the first general-purpose source register, encoded in the "Rn" field.  |

| <wm></wm> | Is the 32-bit name of the second general-purpose source register, encoded in the "Rm" field. |

| <xd></xd> | Is the 64-bit name of the general-purpose destination register, encoded in the "Rd" field.   |

| <xn></xn> | Is the 64-bit name of the first general-purpose source register, encoded in the "Rn" field.  |

| <xm></xm> | Is the 64-bit name of the second general-purpose source register, encoded in the "Rm" field. |

## Operation

```

bits(datasize) result;

bits(datasize) operand1 = X[n, datasize];

bits(datasize) operand2 = X[m, datasize];

(result, -) = AddWithCarry(operand1, operand2, PSTATE.C);

X[d, datasize] = result;

```

## **Operational information**

- The execution time of this instruction is independent of:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

- The response of this instruction to asynchronous exceptions does not vary based on:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

.

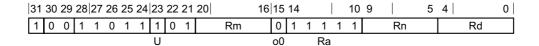

## C6.2.3 ADCS

Add with Carry, setting flags, adds two register values and the Carry flag value, and writes the result to the destination register. It updates the condition flags based on the result.

| 31 30 29 28 | 27 26 25 | 24 23 2 | 2 21 2 | 20 16 | 15 <sup>-</sup> | 14 13 | 3 12 | 11 1 | 0 | 9   5 | 4  | 0 |

|-------------|----------|---------|--------|-------|-----------------|-------|------|------|---|-------|----|---|

| sf 0 1 1    | 101      | 0 0 0   | 0 0    | Rm    | 0               | 0 0   | 0    | 0    | 0 | Rn    | Rd |   |

| op S        |          |         | -      |       |                 |       |      |      |   |       |    |   |

#### 32-bit variant

Applies when sf == 0.

ADCS <Wd>, <Wn>, <Wm>

#### 64-bit variant

Applies when sf == 1.

ADCS <Xd>, <Xn>, <Xm>

### Decode for all variants of this encoding

```

integer d = UInt(Rd);

integer n = UInt(Rn);

integer m = UInt(Rm);

constant integer datasize = 32 << UInt(sf);</pre>

```

### Assembler symbols

| <wd></wd> | Is the 32-bit name of the general-purpose destination register, encoded in the "Rd" field.   |

|-----------|----------------------------------------------------------------------------------------------|

| <wn></wn> | Is the 32-bit name of the first general-purpose source register, encoded in the "Rn" field.  |

| <wm></wm> | Is the 32-bit name of the second general-purpose source register, encoded in the "Rm" field. |

| <xd></xd> | Is the 64-bit name of the general-purpose destination register, encoded in the "Rd" field.   |

| <xn></xn> | Is the 64-bit name of the first general-purpose source register, encoded in the "Rn" field.  |

| <xm></xm> | Is the 64-bit name of the second general-purpose source register, encoded in the "Rm" field. |

## Operation

```

bits(datasize) result;

bits(datasize) operand1 = X[n, datasize];

bits(datasize) operand2 = X[m, datasize];

bits(4) nzcv;

(result, nzcv) = AddWithCarry(operand1, operand2, PSTATE.C);

PSTATE.<N,Z,C,V> = nzcv;

X[d, datasize] = result;

```

## **Operational information**

- The execution time of this instruction is independent of:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

- The response of this instruction to asynchronous exceptions does not vary based on:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

### C6.2.4 ADD (extended register)

Add (extended register) adds a register value and a sign or zero-extended register value, followed by an optional left shift amount, and writes the result to the destination register. The argument that is extended from the <Rm> register can be a byte, halfword, word, or doubleword.

| 31 30 29 28 2 | 27 26 | 25 24 | 23 22 | 21 | 20 16 | 15 13  | 12  10 | 9   5 | 4 0 |

|---------------|-------|-------|-------|----|-------|--------|--------|-------|-----|

| sf 0 0 0      | 1 0   | 1 1   | 0 0   | 1  | Rm    | option | imm3   | Rn    | Rd  |

| op S          |       |       |       |    | -     |        |        | -     | -   |

#### 32-bit variant

Applies when sf == 0.

ADD <Wd|WSP>, <Wn|WSP>, <Wm>{, <extend> {#<amount>}}

#### 64-bit variant

Applies when sf == 1.

ADD <Xd|SP>, <Xn|SP>, <R><m>{, <extend> {#<amount>}}

#### Decode for all variants of this encoding

```

integer d = UInt(Rd);

integer n = UInt(Rn);

integer m = UInt(Rm);

constant integer datasize = 32 << UInt(sf);

ExtendType extend_type = DecodeRegExtend(option);

integer shift = UInt(imm3);

if shift > 4 then UNDEFINED;

```

| <wd wsp></wd wsp> | Is the 32-bi<br>field.                                                                       | it name of the destination general-purpose register or stack pointer, encoded in the "Rd"                    |  |  |  |  |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| <wn wsp></wn wsp> | Is the 32-bi<br>field.                                                                       | Is the 32-bit name of the first source general-purpose register or stack pointer, encoded in the "Rn" field. |  |  |  |  |  |  |  |

| <wm></wm>         | Is the 32-bit name of the second general-purpose source register, encoded in the "Rm" field. |                                                                                                              |  |  |  |  |  |  |  |

| <xd sp></xd sp>   | Is the 64-bi<br>field.                                                                       | Is the 64-bit name of the destination general-purpose register or stack pointer, encoded in the "Rd" field.  |  |  |  |  |  |  |  |

| <xn sp></xn sp>   | Is the 64-bi<br>field.                                                                       | Is the 64-bit name of the first source general-purpose register or stack pointer, encoded in the "Rn" field. |  |  |  |  |  |  |  |

| <r></r>           | Is a width s                                                                                 | specifier, encoded in the "option" field. It can have the following values:                                  |  |  |  |  |  |  |  |

|                   | W                                                                                            | when option = 00x                                                                                            |  |  |  |  |  |  |  |

|                   | W                                                                                            | when option = 010                                                                                            |  |  |  |  |  |  |  |

|                   | Х                                                                                            | when option = x11                                                                                            |  |  |  |  |  |  |  |

|                   | W                                                                                            | when $option = 10x$                                                                                          |  |  |  |  |  |  |  |

|                   | W                                                                                            | when option = 110                                                                                            |  |  |  |  |  |  |  |

| <m></m>           | Is the numb<br>the "Rm" f                                                                    | per [0-30] of the second general-purpose source register or the name ZR (31), encoded in ield.               |  |  |  |  |  |  |  |

<extend> For the 32-bit variant: is the extension to be applied to the second source operand, encoded in the "option" field. It can have the following values:

| UXTB     | when option = $000$ |

|----------|---------------------|

| UXTH     | when option = $001$ |

| LSL UXTW | when option = $010$ |

| UXTX     | when option = $011$ |

| SXTB     | when option = $100$ |

| SXTH     | when option = $101$ |

| SXTW     | when option = $110$ |

| SXTX     | when option = 111   |

If "Rd" or "Rn" is '11111' (WSP) and "option" is '010' then LSL is preferred, but may be omitted when "imm3" is '000'. In all other cases <extend> is required and must be UXTW when "option" is '010'.

For the 64-bit variant: is the extension to be applied to the second source operand, encoded in the "option" field. It can have the following values:

| UXTB     | when option = 000 |

|----------|-------------------|

| UXTH     | when option = 001 |

| UXTW     | when option = 010 |

| LSL UXTX | when option = 011 |

| SXTB     | when option = 100 |

| SXTH     | when option = 101 |

| SXTW     | when option = 110 |

| SXTX     | when option = 111 |

If "Rd" or "Rn" is '11111' (SP) and "option" is '011' then LSL is preferred, but may be omitted when "imm3" is '000'. In all other cases <extend> is required and must be UXTX when "option" is '011'.

<amount> Is the left shift amount to be applied after extension in the range 0 to 4, defaulting to 0, encoded in the "imm3" field. It must be absent when <extend> is absent, is required when <extend> is LSL, and is optional when <extend> is present but not LSL.

## Operation

```

bits(datasize) result;

bits(datasize) operand1 = if n == 31 then SP[]<datasize-1:0> else X[n, datasize];

bits(datasize) operand2 = ExtendReg(m, extend_type, shift, datasize);

(result, -) = AddWithCarry(operand1, operand2, '0');

if d == 31 then

SP[] = ZeroExtend(result, 64);

else

X[d, datasize] = result;

```

## **Operational information**

- The execution time of this instruction is independent of:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

- The response of this instruction to asynchronous exceptions does not vary based on:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

.

### C6.2.5 ADD (immediate)

Add (immediate) adds a register value and an optionally-shifted immediate value, and writes the result to the destination register.

This instruction is used by the alias MOV (to/from SP). See *Alias conditions* for details of when each alias is preferred.

| 31 30 29 28 27 26 25 24 23 22 21 |       | 10 | 9  | 54 | 0 |

|----------------------------------|-------|----|----|----|---|

| sf 0 0 1 0 0 0 1 0 sh            | imm12 |    | Rn | Rd |   |

| op S                             |       |    |    |    |   |

#### 32-bit variant

Applies when sf == 0.

ADD <Wd|WSP>, <Wn|WSP>, #<imm>{, <shift>}

#### 64-bit variant

Applies when sf == 1.

ADD <Xd|SP>, <Xn|SP>, #<imm>{, <shift>}

### Decode for all variants of this encoding

```

integer d = UInt(Rd);

integer n = UInt(Rn);

constant integer datasize = 32 << UInt(sf);

bits(datasize) imm;

case sh of

when '0' imm = ZeroExtend(imm12, datasize);

when '1' imm = ZeroExtend(imm12:Zeros(12), datasize);

```

## Alias conditions

| Alias            | is preferred when                                                       |

|------------------|-------------------------------------------------------------------------|

| MOV (to/from SP) | sh == '0' && imm12 == '00000000000' && (Rd == '11111'    Rn == '11111') |

| <wd wsp></wd wsp>    | Is the 32-bit name of the destination general-purpose register or stack pointer, encoded in the "Rd" field. |

|----------------------|-------------------------------------------------------------------------------------------------------------|

| <wn wsp></wn wsp>    | Is the 32-bit name of the source general-purpose register or stack pointer, encoded in the "Rn" field.      |

| <xd sp></xd sp>      | Is the 64-bit name of the destination general-purpose register or stack pointer, encoded in the "Rd" field. |

| <xn sp=""  =""></xn> | Is the 64-bit name of the source general-purpose register or stack pointer, encoded in the "Rn" field.      |

| <imm></imm>          | Is an unsigned immediate, in the range 0 to 4095, encoded in the "imm12" field.                             |

<shift> Is the optional left shift to apply to the immediate, defaulting to LSL #0 and encoded in the "sh"

field. It can have the following values:

LSL #0 when sh = 0 LSL #12 when sh = 1

## Operation

bits(datasize) result; bits(datasize) operand1 = if n == 31 then SP[]<datasize-1:0> else X[n, datasize]; (result, -) = AddWithCarry(operand1, imm, '0'); if d == 31 then SP[] = ZeroExtend(result, 64); else X[d, datasize] = result;

## **Operational information**

- The execution time of this instruction is independent of:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

- The response of this instruction to asynchronous exceptions does not vary based on:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

## C6.2.6 ADD (shifted register)

Add (shifted register) adds a register value and an optionally-shifted register value, and writes the result to the destination register.

| 3 | 81 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 22 | 21 | 20 16 | 15   | 10 | 9  | 5 | 4  | 0 |

|---|----|----|----|----|----|----|----|----|-------|----|-------|------|----|----|---|----|---|

|   | sf | 0  | 0  | 0  | 1  | 0  | 1  | 1  | shift | 0  | Rm    | imm6 |    | Rn |   | Rd |   |

|   |    | ор | S  | -  |    |    |    |    |       |    |       | -    |    |    |   |    |   |

#### 32-bit variant

Applies when sf == 0.

ADD <Wd>, <Wn>, <Wm>{, <shift> #<amount>}

#### 64-bit variant

Applies when sf == 1.

ADD <Xd>, <Xn>, <Xm>{, <shift> #<amount>}

### Decode for all variants of this encoding

integer d = UInt(Rd); integer n = UInt(Rn); integer m = UInt(Rm); constant integer datasize = 32 << UInt(sf);</pre>

if shift == '11' then UNDEFINED; if sf == '0' && imm6<5> == '1' then UNDEFINED;

```

ShiftType shift_type = DecodeShift(shift);

integer shift_amount = UInt(imm6);

```

| <wd></wd>         | Is the 32-bit                                                                                                       | Is the 32-bit name of the general-purpose destination register, encoded in the "Rd" field.                                       |  |  |  |  |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| <wn></wn>         | Is the 32-bit                                                                                                       | Is the 32-bit name of the first general-purpose source register, encoded in the "Rn" field.                                      |  |  |  |  |  |  |  |

| <wm></wm>         | Is the 32-bit                                                                                                       | name of the second general-purpose source register, encoded in the "Rm" field.                                                   |  |  |  |  |  |  |  |

| <xd></xd>         | Is the 64-bit                                                                                                       | name of the general-purpose destination register, encoded in the "Rd" field.                                                     |  |  |  |  |  |  |  |

| <xn></xn>         | Is the 64-bit                                                                                                       | name of the first general-purpose source register, encoded in the "Rn" field.                                                    |  |  |  |  |  |  |  |

| <xm></xm>         | Is the 64-bit                                                                                                       | name of the second general-purpose source register, encoded in the "Rm" field.                                                   |  |  |  |  |  |  |  |

| <shift></shift>   | -                                                                                                                   | al shift type to be applied to the second source operand, defaulting to LSL and encoded field. It can have the following values: |  |  |  |  |  |  |  |

|                   | LSL                                                                                                                 | when shift = 00                                                                                                                  |  |  |  |  |  |  |  |

|                   | LSR                                                                                                                 | when shift = 01                                                                                                                  |  |  |  |  |  |  |  |

|                   | ASR                                                                                                                 | when shift = 10                                                                                                                  |  |  |  |  |  |  |  |

|                   | The encoding shift = 11 is reserved.                                                                                |                                                                                                                                  |  |  |  |  |  |  |  |

| <amount></amount> | For the 32-bit variant: is the shift amount, in the range 0 to 31, defaulting to 0 and encoded in the "imm6" field. |                                                                                                                                  |  |  |  |  |  |  |  |

For the 64-bit variant: is the shift amount, in the range 0 to 63, defaulting to 0 and encoded in the "imm6" field.

## Operation

```

bits(datasize) result;

bits(datasize) operand1 = X[n, datasize];

bits(datasize) operand2 = ShiftReg(m, shift_type, shift_amount, datasize);

(result, -) = AddWithCarry(operand1, operand2, '0');

X[d, datasize] = result;

```

## **Operational information**

- The execution time of this instruction is independent of:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

- The response of this instruction to asynchronous exceptions does not vary based on:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

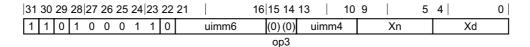

## C6.2.7 ADDG

Add with Tag adds an immediate value scaled by the Tag granule to the address in the source register, modifies the Logical Address Tag of the address using an immediate value, and writes the result to the destination register. Tags specified in GCR\_EL1.Exclude are excluded from the possible outputs when modifying the Logical Address Tag.

### Integer

(FEAT\_MTE)

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 1     | 16 15 14 | 13    | 10 | 9 | 5 | 4 |    | 0 |

|----|----|----|----|----|----|----|----|----|----|-------|----------|-------|----|---|---|---|----|---|

| 1  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 1  | 0  | uimm6 | (0)(0)   | uimm4 | 4  | X | ı |   | Xd |   |

|    |    |    |    |    |    |    |    |    |    |       | 6qo      |       |    |   |   | - |    |   |

#### Encoding

ADDG <Xd|SP>, <Xn|SP>, #<uimm6>, #<uimm4>

#### Decode for this encoding

if !IsFeatureImplemented(FEAT\_MTE) then UNDEFINED; integer d = UInt(Xd); integer n = UInt(Xn); bits(64) offset = LSL(ZeroExtend(uimm6, 64), LOG2\_TAG\_GRANULE);

## Assembler symbols

| <xd sp></xd sp>      | Is the 64-bit name of the destination general-purpose register or stack pointer, encoded in the "Xd" field. |

|----------------------|-------------------------------------------------------------------------------------------------------------|

| <xn sp=""  =""></xn> | Is the 64-bit name of the source general-purpose register or stack pointer, encoded in the "Xn" field.      |

| <uimm6></uimm6>      | Is an unsigned immediate, a multiple of 16 in the range 0 to 1008, encoded in the "uimm6" field.            |

| <uimm4></uimm4>      | Is an unsigned immediate, in the range 0 to 15, encoded in the "uimm4" field.                               |

## Operation

```

bits(64) operand1 = if n == 31 then SP[] else X[n, 64];

bits(4) start_tag = AArch64.AllocationTagFromAddress(operand1);

bits(16) exclude = GCR_EL1.Exclude;

bits(64) result;

bits(64) result;

bits(4) rtag;

if AArch64.AllocationTagAccessIsEnabled(PSTATE.EL) then

rtag = AArch64.ChooseNonExcludedTag(start_tag, uimm4, exclude);

else

rtag = '0000';

(result, -) = AddWithCarry(operand1, offset, '0');

result = AArch64.AddressWithAllocationTag(result, rtag);

if d == 31 then

SP[] = result;

else

X[d, 64] = result;

```

## C6.2.8 ADDS (extended register)

Add (extended register), setting flags, adds a register value and a sign or zero-extended register value, followed by an optional left shift amount, and writes the result to the destination register. The argument that is extended from the <Rm> register can be a byte, halfword, word, or doubleword. It updates the condition flags based on the result.

This instruction is used by the alias CMN (extended register). See Alias conditions for details of when each alias is preferred.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 16 | 15 13  | 12  10 | 9   5 | 4  | 0 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|--------|--------|-------|----|---|

| sf | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 0  | 0  | 1  | Rm |    | option | imm3   | Rn    | Rd |   |

|    | ор | S  |    |    |    |    |    |    |    |    |    |    |        |        |       |    |   |

#### 32-bit variant

Applies when sf == 0.

ADDS <Wd>, <Wn|WSP>, <Wm>{, <extend> {#<amount>}}

#### 64-bit variant

Applies when sf == 1.

ADDS <Xd>, <Xn|SP>, <R><m>{, <extend> {#<amount>}}

#### Decode for all variants of this encoding

integer d = UInt(Rd); integer n = UInt(Rn); integer m = UInt(Rm); constant integer datasize = 32 << UInt(sf); ExtendType extend\_type = DecodeRegExtend(option); integer shift = UInt(imm3); if shift > 4 then UNDEFINED;

### Alias conditions

| Alias                   | is preferred when |

|-------------------------|-------------------|

| CMN (extended register) | Rd == '11111'     |

| <wd></wd>            | Is the 32-bit name of the general-purpose destination register, encoded in the "Rd" field.                   |  |  |  |  |  |  |

|----------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| <wn wsp></wn wsp>    | Is the 32-bit name of the first source general-purpose register or stack pointer, encoded in the field.      |  |  |  |  |  |  |

| <wm></wm>            | Is the 32-bit name of the second general-purpose source register, encoded in the "Rm" field.                 |  |  |  |  |  |  |

| <xd></xd>            | Is the 64-bit name of the general-purpose destination register, encoded in the "Rd" field.                   |  |  |  |  |  |  |

| <xn sp=""  =""></xn> | Is the 64-bit name of the first source general-purpose register or stack pointer, encoded in the "Rn" field. |  |  |  |  |  |  |

| <r></r>              | Is a width specifier, encoded in the "option" field. It can have the following values:                       |  |  |  |  |  |  |

|                      | W when $option = 00x$                                                                                        |  |  |  |  |  |  |

| W | when $option = 010$ |

|---|---------------------|

| Х | when option = $x11$ |

| W | when option = $10x$ |

| W | when $option = 110$ |

Is the number [0-30] of the second general-purpose source register or the name ZR (31), encoded in the "Rm" field.

<extend> For the 32-bit variant: is the extension to be applied to the second source operand, encoded in the "option" field. It can have the following values:

| UXTB     | when option = $000$ |

|----------|---------------------|

| UXTH     | when option = $001$ |

| LSL UXTW | when option = $010$ |

| UXTX     | when option = $011$ |

| SXTB     | when option = 100   |

| SXTH     | when option = 101   |

| SXTW     | when option = $110$ |

| SXTX     | when option = 111   |

|          |                     |

If "Rn" is '11111' (WSP) and "option" is '010' then LSL is preferred, but may be omitted when "imm3" is '000'. In all other cases <extend> is required and must be UXTW when "option" is '010'.

For the 64-bit variant: is the extension to be applied to the second source operand, encoded in the "option" field. It can have the following values:

| UXTB     | when $\ensuremath{option}$ | = | 000 |

|----------|----------------------------|---|-----|

| UXTH     | when option                | = | 001 |

| UXTW     | when $option$              | = | 010 |

| LSL UXTX | when $option$              | = | 011 |

| SXTB     | when $option$              | = | 100 |

| SXTH     | when $option$              | = | 101 |

| SXTW     | when $option$              | = | 110 |

| SXTX     | when option                | = | 111 |

If "Rn" is '11111' (SP) and "option" is '011' then LSL is preferred, but may be omitted when "imm3" is '000'. In all other cases <extend> is required and must be UXTX when "option" is '011'.

<amount> Is the left shift amount to be applied after extension in the range 0 to 4, defaulting to 0, encoded in the "imm3" field. It must be absent when <extend> is absent, is required when <extend> is LSL, and is optional when <extend> is present but not LSL.

## Operation

<m>

```

bits(datasize) result;

bits(datasize) operand1 = if n == 31 then SP[]<datasize-1:0> else X[n, datasize];

bits(datasize) operand2 = ExtendReg(m, extend_type, shift, datasize);

bits(4) nzcv;

(result, nzcv) = AddWithCarry(operand1, operand2, '0');

PSTATE.<N,Z,C,V> = nzcv;

X[d, datasize] = result;

```

## **Operational information**

- The execution time of this instruction is independent of:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

- The response of this instruction to asynchronous exceptions does not vary based on:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

### C6.2.9 ADDS (immediate)

Add (immediate), setting flags, adds a register value and an optionally-shifted immediate value, and writes the result to the destination register. It updates the condition flags based on the result.

This instruction is used by the alias CMN (immediate). See *Alias conditions* for details of when each alias is preferred.

| 31 30 29 28 27 26 25 24 23 22 21 | 10    | 9   5 | 4   0 |

|----------------------------------|-------|-------|-------|

| sf 0 1 1 0 0 0 1 0 sh            | imm12 | Rn    | Rd    |

| op S                             |       |       |       |

#### 32-bit variant

Applies when sf == 0.

ADDS <Wd>, <Wn|WSP>, #<imm>{, <shift>}

#### 64-bit variant

Applies when sf == 1.

ADDS <Xd>, <Xn|SP>, #<imm>{, <shift>}

### Decode for all variants of this encoding

```

integer d = UInt(Rd);

integer n = UInt(Rn);

constant integer datasize = 32 << UInt(sf);

bits(datasize) imm;

case sh of

when '0' imm = ZeroExtend(imm12, datasize);

when '1' imm = ZeroExtend(imm12:Zeros(12), datasize);

```

## Alias conditions

| Alias           | is preferred when |

|-----------------|-------------------|

| CMN (immediate) | Rd == '11111'     |

| <wd></wd>            | Is the 32-bit name of the general-purpose destination register, encoded in the "Rd" field.                                                  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| <wn wsp></wn wsp>    | Is the 32-bit name of the source general-purpose register or stack pointer, encoded in the "Rn" field.                                      |

| <xd></xd>            | Is the 64-bit name of the general-purpose destination register, encoded in the "Rd" field.                                                  |

| <xn sp=""  =""></xn> | Is the 64-bit name of the source general-purpose register or stack pointer, encoded in the "Rn" field.                                      |

| <imm></imm>          | Is an unsigned immediate, in the range 0 to 4095, encoded in the "imm12" field.                                                             |

| <shift></shift>      | Is the optional left shift to apply to the immediate, defaulting to LSL #0 and encoded in the "sh" field. It can have the following values: |

|                      | LSL #0 when sh = 0                                                                                                                          |

|                      | LSL #12 when sh = 1                                                                                                                         |

|                      |                                                                                                                                             |

## Operation

```

bits(datasize) result;

bits(datasize) operand1 = if n == 31 then SP[]<datasize-1:0> else X[n, datasize];

bits(4) nzcv;

(result, nzcv) = AddWithCarry(operand1, imm, '0');

PSTATE.<N,Z,C,V> = nzcv;

X[d, datasize] = result;

```

## **Operational information**

- The execution time of this instruction is independent of:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

- The response of this instruction to asynchronous exceptions does not vary based on:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

### C6.2.10 ADDS (shifted register)

Add (shifted register), setting flags, adds a register value and an optionally-shifted register value, and writes the result to the destination register. It updates the condition flags based on the result.

This instruction is used by the alias CMN (shifted register). See *Alias conditions* for details of when each alias is preferred.

| 31 30 29 28 | 27 26 | 25 24 | 23 22 2 | 1 20 | 16 | 15   | 10 | 9  | 5 | 4  | 0 |

|-------------|-------|-------|---------|------|----|------|----|----|---|----|---|

| sf 0 1 0    | 1 0   | 1 1   | shift   | )    | Rm | imm6 |    | Rn |   | Rd |   |

| op S        |       |       |         |      |    |      |    |    |   |    |   |

#### 32-bit variant

Applies when sf == 0.

ADDS <Wd>, <Wn>, <Wm>{, <shift> #<amount>}

#### 64-bit variant

Applies when sf == 1.

ADDS <Xd>, <Xn>, <Xm>{, <shift> #<amount>}

### Decode for all variants of this encoding

integer d = UInt(Rd); integer n = UInt(Rn); integer m = UInt(Rm); constant integer datasize = 32 << UInt(sf);</pre>

if shift == '11' then UNDEFINED; if sf == '0' && imm6<5> == '1' then UNDEFINED;

ShiftType shift\_type = DecodeShift(shift); integer shift\_amount = UInt(imm6);

## Alias conditions

| Alias                  | is preferred when |

|------------------------|-------------------|

| CMN (shifted register) | Rd == '11111'     |

| <wd></wd> | Is the 32-bit name of the general-purpose destination register, encoded in the "Rd" field.   |

|-----------|----------------------------------------------------------------------------------------------|

| <wn></wn> | Is the 32-bit name of the first general-purpose source register, encoded in the "Rn" field.  |

| <wm></wm> | Is the 32-bit name of the second general-purpose source register, encoded in the "Rm" field. |

| <xd></xd> | Is the 64-bit name of the general-purpose destination register, encoded in the "Rd" field.   |

| <xn></xn> | Is the 64-bit name of the first general-purpose source register, encoded in the "Rn" field.  |

| <xm></xm> | Is the 64-bit name of the second general-purpose source register, encoded in the "Rm" field. |

|           |                                                                                              |

<shift> Is the optional shift type to be applied to the second source operand, defaulting to LSL and encoded in the "shift" field. It can have the following values:

| LSL      | when $shift = 00$ |

|----------|-------------------|

| LSR      | when $shift = 01$ |

| ASR      | when $shift = 10$ |

| <b>T</b> | 1. 1.1.6. 44      |

The encoding shift = 11 is reserved.

<amount> For the 32-bit variant: is the shift amount, in the range 0 to 31, defaulting to 0 and encoded in the

"imm6" field.

For the 64-bit variant: is the shift amount, in the range 0 to 63, defaulting to 0 and encoded in the "imm6" field.

## Operation

```

bits(datasize) result;

bits(datasize) operand1 = X[n, datasize];

bits(datasize) operand2 = ShiftReg(m, shift_type, shift_amount, datasize);

bits(4) nzcv;

(result, nzcv) = AddWithCarry(operand1, operand2, '0');

PSTATE.<N,Z,C,V> = nzcv;

X[d, datasize] = result;

```

## **Operational information**

- The execution time of this instruction is independent of:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

- The response of this instruction to asynchronous exceptions does not vary based on:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

## C6.2.11 ADR

Form PC-relative address adds an immediate value to the PC value to form a PC-relative address, and writes the result to the destination register.

| 31 | 30 29 | 28 | 27 | 26 | 25 | 24 | 23 |  |       |  | 5 | 4 |    | 0 |

|----|-------|----|----|----|----|----|----|--|-------|--|---|---|----|---|

| 0  | immlo | 1  | 0  | 0  | 0  | 0  |    |  | immhi |  |   |   | Rd |   |

#### Encoding

ADR <Xd>, <1abe1>

#### Decode for this encoding

integer d = UInt(Rd); bits(64) imm;

imm = SignExtend(immhi:immlo, 64);

## **Assembler symbols**

<Xd> Is the 64-bit name of the general-purpose destination register, encoded in the "Rd" field.

label> Is the program label whose address is to be calculated. Its offset from the address of this instruction, in the range +/-1MB, is encoded in "immhi:immlo".

## Operation

X[d, 64] = PC64 + imm;

## C6.2.12 ADRP

Form PC-relative address to 4KB page adds an immediate value that is shifted left by 12 bits, to the PC value to form a PC-relative address, with the bottom 12 bits masked out, and writes the result to the destination register.

| 31 30 29 28 27 26 25 24 23 |       |  | 5 4 | C  | ) |

|----------------------------|-------|--|-----|----|---|

| 1 immlo 1 0 0 0 0          | immhi |  |     | Rd |   |

#### Encoding

ADRP <Xd>, <1abe1>

#### Decode for this encoding

integer d = UInt(Rd); bits(64) imm;

imm = SignExtend(immhi:immlo:Zeros(12), 64);

## **Assembler symbols**

<Xd> Is the 64-bit name of the general-purpose destination register, encoded in the "Rd" field.

Is the program label whose 4KB page address is to be calculated. Its offset from the page address of this instruction, in the range +/-4GB, is encoded as "immhi:immlo" times 4096.

## Operation

bits(64) base = PC64<63:12>:Zeros(12); X[d, 64] = base + imm;

## C6.2.13 AND (immediate)

Bitwise AND (immediate) performs a bitwise AND of a register value and an immediate value, and writes the result to the destination register.

| 3 | 1  | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 1   16 | 6 15 | 10 | 9 | 5  | 4 |    | 0 |

|---|----|----|----|----|----|----|----|----|----|----|--------|------|----|---|----|---|----|---|

| s | sf | 0  | 0  | 1  | 0  | 0  | 1  | 0  | 0  | Ν  | immr   | imms | 6  |   | Rn |   | Rd |   |

|   |    | o  | эс | -  |    |    |    |    |    |    |        |      |    |   |    |   |    |   |

#### 32-bit variant

Applies when sf == 0 & N == 0.

AND <Wd|WSP>, <Wn>, #<imm>

#### 64-bit variant

Applies when sf == 1.

AND <Xd|SP>, <Xn>, #<imm>

### Decode for all variants of this encoding

```

integer d = UInt(Rd);

integer n = UInt(Rn);

constant integer datasize = 32 << UInt(sf);

bits(datasize) imm;

if sf == '0' && N != '0' then UNDEFINED;

(imm, -) = DecodeBitMasks(N, imms, immr, TRUE, datasize);

```

## **Assembler symbols**

| <wd wsp></wd wsp> | Is the 32-bit name of the destination general-purpose register or stack pointer, encoded in the "Rd" field.                                              |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| <wn></wn>         | Is the 32-bit name of the general-purpose source register, encoded in the "Rn" field.                                                                    |

| <xd sp></xd sp>   | Is the 64-bit name of the destination general-purpose register or stack pointer, encoded in the "Rd" field.                                              |

| <xn></xn>         | Is the 64-bit name of the general-purpose source register, encoded in the "Rn" field.                                                                    |

| <imm></imm>       | For the 32-bit variant: is the bitmask immediate, encoded in "imms:immr".<br>For the 64-bit variant: is the bitmask immediate, encoded in "N:imms:immr". |

## Operation

```

bits(datasize) result;

bits(datasize) operand1 = X[n, datasize];

result = operand1 AND imm;

if d == 31 then

SP[] = ZeroExtend(result, 64);

else

X[d, datasize] = result;

```

## **Operational information**

- The execution time of this instruction is independent of:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

- The response of this instruction to asynchronous exceptions does not vary based on:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

## C6.2.14 AND (shifted register)

Bitwise AND (shifted register) performs a bitwise AND of a register value and an optionally-shifted register value, and writes the result to the destination register.

| 31 30 29 28 27 26 25 24 23 22 21 20 |     |   |   |   |   |   |       | 21 | 20 16 | 15   | 10 | 9 | :  | 54 |    | 0 |

|-------------------------------------|-----|---|---|---|---|---|-------|----|-------|------|----|---|----|----|----|---|

| sf                                  | 0 0 | 0 | 1 | 0 | 1 | 0 | shift | 0  | Rm    | imm6 |    |   | Rn |    | Rd |   |

|                                     | орс |   |   |   |   |   |       | Ν  | -     |      |    |   |    |    |    |   |

#### 32-bit variant

Applies when sf == 0.

AND <Wd>, <Wn>, <Wm>{, <shift> #<amount>}

#### 64-bit variant

Applies when sf == 1.

AND <Xd>, <Xn>, <Xm>{, <shift> #<amount>}

### Decode for all variants of this encoding

integer d = UInt(Rd); integer n = UInt(Rn); integer m = UInt(Rm); constant integer datasize = 32 << UInt(sf); if sf == '0' && imm6<5> == '1' then UNDEFINED;

ShiftType shift\_type = DecodeShift(shift); integer shift\_amount = UInt(imm6);

| <wd></wd>         | Is the 32-bit name of the general-purpose destination register, encoded in the "Rd" field.                                                     |  |  |  |  |  |  |  |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| <wn></wn>         | Is the 32-bit name of the first general-purpose source register, encoded in the "Rn" field.                                                    |  |  |  |  |  |  |  |  |  |

| <wm></wm>         | Is the 32-bit name of the second general-purpose source register, encoded in the "Rm" field.                                                   |  |  |  |  |  |  |  |  |  |

| <xd></xd>         | Is the 64-bit name of the general-purpose destination register, encoded in the "Rd" field.                                                     |  |  |  |  |  |  |  |  |  |

| <xn></xn>         | Is the 64-bit name of the first general-purpose source register, encoded in the "Rn" field.                                                    |  |  |  |  |  |  |  |  |  |

| <xm></xm>         | Is the 64-bit name of the second general-purpose source register, encoded in the "Rm" field.                                                   |  |  |  |  |  |  |  |  |  |

| <shift></shift>   | Is the optional shift to be applied to the final source, defaulting to LSL and encoded in the "shift" field. It can have the following values: |  |  |  |  |  |  |  |  |  |

|                   | LSL when shift = 00                                                                                                                            |  |  |  |  |  |  |  |  |  |

|                   | LSR when shift = 01                                                                                                                            |  |  |  |  |  |  |  |  |  |

|                   | ASR when shift = 10                                                                                                                            |  |  |  |  |  |  |  |  |  |

|                   | ROR when shift = 11                                                                                                                            |  |  |  |  |  |  |  |  |  |

| <amount></amount> | For the 32-bit variant: is the shift amount, in the range 0 to 31, defaulting to 0 and encoded in the "imm6" field.                            |  |  |  |  |  |  |  |  |  |

|                   | For the 64-bit variant: is the shift amount, in the range 0 to 63, defaulting to 0 and encoded in the "imm6" field,                            |  |  |  |  |  |  |  |  |  |

## Operation

```

bits(datasize) operand1 = X[n, datasize];

bits(datasize) operand2 = ShiftReg(m, shift_type, shift_amount, datasize);

bits(datasize) result;

result = operand1 AND operand2;

X[d, datasize] = result;

```

## **Operational information**

- The execution time of this instruction is independent of:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

- The response of this instruction to asynchronous exceptions does not vary based on:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

### C6.2.15 ANDS (immediate)

Bitwise AND (immediate), setting flags, performs a bitwise AND of a register value and an immediate value, and writes the result to the destination register. It updates the condition flags based on the result.

This instruction is used by the alias TST (immediate). See *Alias conditions* for details of when each alias is preferred.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21   16 | 6 15 | 10 | 9   5 | 54 | 0 |

|----|----|----|----|----|----|----|----|----|----|---------|------|----|-------|----|---|

| sf | 1  | 1  | 1  | 0  | 0  | 1  | 0  | 0  | Ν  | immr    | imms |    | Rn    | Rd |   |

|    | op | oc |    |    |    |    |    |    |    |         |      |    |       |    |   |

#### 32-bit variant

Applies when sf == 0 & N == 0.

ANDS <Wd>, <Wn>, #<imm>

#### 64-bit variant

Applies when sf == 1.

ANDS <Xd>, <Xn>, #<imm>

### Decode for all variants of this encoding

integer d = UInt(Rd); integer n = UInt(Rn); constant integer datasize = 32 << UInt(sf);</pre>

bits(datasize) imm; if sf == '0' && N != '0' then UNDEFINED; (imm, -) = DecodeBitMasks(N, imms, immr, TRUE, datasize);

## Alias conditions

| Alias           | is preferred when |

|-----------------|-------------------|

| TST (immediate) | Rd == '11111'     |

| <wd></wd>   | Is the 32-bit name of the general-purpose destination register, encoded in the "Rd" field. |

|-------------|--------------------------------------------------------------------------------------------|

| <wn></wn>   | Is the 32-bit name of the general-purpose source register, encoded in the "Rn" field.      |

| <xd></xd>   | Is the 64-bit name of the general-purpose destination register, encoded in the "Rd" field. |

| <xn></xn>   | Is the 64-bit name of the general-purpose source register, encoded in the "Rn" field.      |

| <imm></imm> | For the 32-bit variant: is the bitmask immediate, encoded in "imms:immr".                  |

|             | For the 64-bit variant: is the bitmask immediate, encoded in "N:imms:immr".                |

## Operation

```

bits(datasize) result;

bits(datasize) operand1 = X[n, datasize];

result = operand1 AND imm;

PSTATE.<N,Z,C,V> = result<datasize-1>:IsZeroBit(result):'00';

```

X[d, datasize] = result;

## **Operational information**

- The execution time of this instruction is independent of:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

- The response of this instruction to asynchronous exceptions does not vary based on:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

### C6.2.16 ANDS (shifted register)

Bitwise AND (shifted register), setting flags, performs a bitwise AND of a register value and an optionally-shifted register value, and writes the result to the destination register. It updates the condition flags based on the result.

This instruction is used by the alias TST (shifted register). See *Alias conditions* for details of when each alias is preferred.

| 31 30 29 | 28 | 27 | 26 | 25 | 24 | 23 22 | 21 | 20  16 | 15   | 10 | 9 |    | 5 | 4  | 0 |

|----------|----|----|----|----|----|-------|----|--------|------|----|---|----|---|----|---|

| sf 1 1   | 0  | 1  | 0  | 1  | 0  | shift | 0  | Rm     | imm6 |    |   | Rn |   | Rd |   |

| opc      |    |    |    |    |    |       | Ν  |        |      |    |   |    |   |    |   |

#### 32-bit variant

Applies when sf == 0.

ANDS <Wd>, <Wn>, <Wm>{, <shift> #<amount>}

#### 64-bit variant

Applies when sf == 1.

ANDS <Xd>, <Xn>, <Xm>{, <shift> #<amount>}

### Decode for all variants of this encoding

integer d = UInt(Rd); integer n = UInt(Rn); integer m = UInt(Rm); constant integer datasize = 32 << UInt(sf); if sf == '0' && imm6<5> == '1' then UNDEFINED; ShiftType shift\_type = DecodeShift(shift); integer shift\_amount = UInt(imm6);

### Alias conditions

| Alias                  | is preferred when |

|------------------------|-------------------|

| TST (shifted register) | Rd == '11111'     |

| <wd></wd> | Is the 32-bit name of the general-purpose destination register, encoded in the "Rd" field.   |

|-----------|----------------------------------------------------------------------------------------------|

| <wn></wn> | Is the 32-bit name of the first general-purpose source register, encoded in the "Rn" field.  |

| <wm></wm> | Is the 32-bit name of the second general-purpose source register, encoded in the "Rm" field. |

| <xd></xd> | Is the 64-bit name of the general-purpose destination register, encoded in the "Rd" field.   |

| <xn></xn> | Is the 64-bit name of the first general-purpose source register, encoded in the "Rn" field.  |

| <xm></xm> | Is the 64-bit name of the second general-purpose source register, encoded in the "Rm" field. |

|           |                                                                                              |

<shift> Is the optional shift to be applied to the final source, defaulting to LSL and encoded in the "shift" field. It can have the following values:

| LSL | when shift = $00$ |

|-----|-------------------|

| LSR | when $shift = 01$ |

| ASR | when $shift = 10$ |

| ROR | when shift = 11   |

<amount> For the 32-bit variant: is the shift amount, in the range 0 to 31, defaulting to 0 and encoded in the

"imm6" field.

For the 64-bit variant: is the shift amount, in the range 0 to 63, defaulting to 0 and encoded in the "imm6" field,

## Operation

```

bits(datasize) operand1 = X[n, datasize];

bits(datasize) operand2 = ShiftReg(m, shift_type, shift_amount, datasize);

bits(datasize) result;

```

```

result = operand1 AND operand2;

PSTATE.<N,Z,C,V> = result<datasize-1>:IsZeroBit(result):'00';

```

```

X[d, datasize] = result;

```

## **Operational information**

- The execution time of this instruction is independent of:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

- The response of this instruction to asynchronous exceptions does not vary based on:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

## C6.2.17 ASR (register)

Arithmetic Shift Right (register) shifts a register value right by a variable number of bits, shifting in copies of its sign bit, and writes the result to the destination register. The remainder obtained by dividing the second source register by the data size defines the number of bits by which the first source register is right-shifted.

This instruction is an alias of the ASRV instruction. This means that:

- The encodings in this description are named to match the encodings of ASRV.

- The description of ASRV gives the operational pseudocode, any CONSTRAINED UNPREDICTABLE behavior, and any operational information for this instruction.

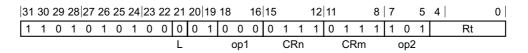

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 5 | 4 |    | 0 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|----|---|

| sf | 0  | 0  | 1  | 1  | 0  | 1  | 0  | 1  | 1  | 0  | Rm |    | 0  | 0  | 1  | 0  | 1  | 0  | R | n |   | Rd |   |

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 01 | n2 |   |   |   |    |   |

#### 32-bit variant

Applies when sf == 0.

ASR <Wd>, <Wn>, <Wm>

is equivalent to

ASRV <Wd>, <Wn>, <Wm>

and is always the preferred disassembly.

### 64-bit variant

Applies when sf == 1.

ASR <Xd>, <Xn>, <Xm>

is equivalent to

ASRV <Xd>, <Xn>, <Xm>

and is always the preferred disassembly.

#### Assembler symbols

| <wd></wd> | Is the 32-bit name of the general-purpose destination register, encoded in the "Rd" field.                                                            |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| <wn></wn> | Is the 32-bit name of the first general-purpose source register, encoded in the "Rn" field.                                                           |

| <wm></wm> | Is the 32-bit name of the second general-purpose source register holding a shift amount from 0 to 31 in its bottom 5 bits, encoded in the "Rm" field. |

| <xd></xd> | Is the 64-bit name of the general-purpose destination register, encoded in the "Rd" field.                                                            |

| <xn></xn> | Is the 64-bit name of the first general-purpose source register, encoded in the "Rn" field.                                                           |

| <xm></xm> | Is the 64-bit name of the second general-purpose source register holding a shift amount from 0 to 63 in its bottom 6 bits, encoded in the "Rm" field. |

## Operation

The description of ASRV gives the operational pseudocode for this instruction.

# **Operational information**

- The execution time of this instruction is independent of:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

- The response of this instruction to asynchronous exceptions does not vary based on:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

# C6.2.18 ASR (immediate)

Arithmetic Shift Right (immediate) shifts a register value right by an immediate number of bits, shifting in copies of the sign bit in the upper bits and zeros in the lower bits, and writes the result to the destination register.

This instruction is an alias of the **SBFM** instruction. This means that:

- The encodings in this description are named to match the encodings of SBFM.

- The description of SBFM gives the operational pseudocode, any CONSTRAINED UNPREDICTABLE behavior, and any operational information for this instruction.

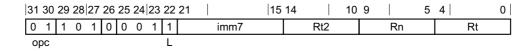

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 1   16 | 6 1 | 5 |   |    |    |   | 10 | 9  | 5 | 4  | 0 |

|----|----|----|----|----|----|----|----|----|----|--------|-----|---|---|----|----|---|----|----|---|----|---|

| sf | 0  | 0  | 1  | 0  | 0  | 1  | 1  | 0  | Ν  | immr   | >   | ĸ | 1 | 1  | 1  | 1 | 1  | Rn |   | Rd |   |

|    | op | C  |    |    |    |    |    |    |    |        |     |   |   | im | ms |   |    |    |   |    |   |

### 32-bit variant

Applies when sf == 0 && N == 0 && imms == 011111.

ASR <Wd>, <Wn>, #<shift>

is equivalent to

SBFM <Wd>>, <Wn>, #<shift>, #31

and is always the preferred disassembly.

#### 64-bit variant

Applies when sf == 1 && N == 1 && imms == 111111. ASR <Xd>, <Xn>, #<shift>

is equivalent to

SBFM <Xd>, <Xn>, #<shift>, #63

and is always the preferred disassembly.

### Assembler symbols

| <wd></wd>       | Is the 32-bit name of the general-purpose destination register, encoded in the "Rd" field.      |

|-----------------|-------------------------------------------------------------------------------------------------|

| <wn></wn>       | Is the 32-bit name of the general-purpose source register, encoded in the "Rn" field.           |

| <xd></xd>       | Is the 64-bit name of the general-purpose destination register, encoded in the "Rd" field.      |

| <xn></xn>       | Is the 64-bit name of the general-purpose source register, encoded in the "Rn" field.           |

| <shift></shift> | For the 32-bit variant: is the shift amount, in the range 0 to 31, encoded in the "immr" field. |

|                 | For the 64-bit variant: is the shift amount, in the range 0 to 63, encoded in the "immr" field. |

### Operation

The description of SBFM gives the operational pseudocode for this instruction.

# **Operational information**

- The execution time of this instruction is independent of:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

- The response of this instruction to asynchronous exceptions does not vary based on:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

# C6.2.19 ASRV

Arithmetic Shift Right Variable shifts a register value right by a variable number of bits, shifting in copies of its sign bit, and writes the result to the destination register. The remainder obtained by dividing the second source register by the data size defines the number of bits by which the first source register is right-shifted.

This instruction is used by the alias ASR (register). The alias is always the preferred disassembly.

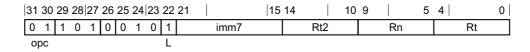

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 5 | 4 |    | 0 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|----|---|

| sf | 0  | 0  | 1  | 1  | 0  | 1  | 0  | 1  | 1  | 0  | Rm |    | 0  | 0  | 1  | 0  | 1  | 0  | Rr | l |   | Rd |   |

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 0  | o2 |    |   | - |    |   |

#### 32-bit variant

Applies when sf == 0.

ASRV <Wd>, <Wn>, <Wm>

#### 64-bit variant

Applies when sf == 1.

ASRV <Xd>, <Xn>, <Xm>

### Decode for all variants of this encoding

integer d = UInt(Rd); integer n = UInt(Rn); integer m = UInt(Rm); constant integer datasize = 32 << UInt(sf); ShiftType shift\_type = DecodeShift(op2);

### Assembler symbols

| <wd></wd> | Is the 32-bit name of the general-purpose destination register, encoded in the "Rd" field.                                                            |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| <wn></wn> | Is the 32-bit name of the first general-purpose source register, encoded in the "Rn" field.                                                           |

| <wm></wm> | Is the 32-bit name of the second general-purpose source register holding a shift amount from 0 to 31 in its bottom 5 bits, encoded in the "Rm" field. |

| <xd></xd> | Is the 64-bit name of the general-purpose destination register, encoded in the "Rd" field.                                                            |

| <xn></xn> | Is the 64-bit name of the first general-purpose source register, encoded in the "Rn" field.                                                           |

| <xm></xm> | Is the 64-bit name of the second general-purpose source register holding a shift amount from 0 to 63 in its bottom 6 bits, encoded in the "Rm" field. |

# Operation

```

bits(datasize) result;

bits(datasize) operand2 = X[m, datasize];

result = ShiftReg(n, shift_type, UInt(operand2) MOD datasize, datasize);

X[d, datasize] = result;

```

# **Operational information**

- The execution time of this instruction is independent of:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

- The response of this instruction to asynchronous exceptions does not vary based on:

- The values of the data supplied in any of its registers.

- The values of the NZCV flags.

#### C6.2.20 AT

Address Translate. For more information, see op0==0b01, cache maintenance, TLB maintenance, address translation, prediction restriction, BRBE, Trace Extension, and Guarded Control Stack instructions.

This instruction is an alias of the SYS instruction. This means that:

- The encodings in this description are named to match the encodings of SYS.

- The description of SYS gives the operational pseudocode, any CONSTRAINED UNPREDICTABLE behavior, and any operational information for this instruction.

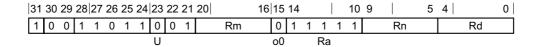

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 16  | 15 |    |    | 12 | 11 |    |    | 8 | 7 5 | 4 |    | 0 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|----|---|-----|---|----|---|

| 1  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 1  | c  | pp1 | 0  | 1  | 1  | 1  | 1  | 0  | 0  | х | op2 |   | Rt |   |

|    |    |    |    |    |    |    |    |    |    | L  |    |    |    |     |    | CF | Rn |    |    | CF | ٢m |   |     |   |    |   |

### Encoding

AT <at\_op>, <Xt>

is equivalent to

SYS #<op1>, C7, <Cm>, #<op2>, <Xt>

and is the preferred disassembly when SysOp(op1, '0111', CRm, op2) == Sys\_AT.

### Assembler symbols

| <at_op></at_op> |              | nstruction name, as listed for the AT system instruction group, encoded in the n<0>:op2" field. It can have the following values: |

|-----------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------|

|                 | S1E1R        | when op1 = 000, CRm<0> = 0, op2 = 000                                                                                             |

|                 | S1E1W        | when op1 = 000, CRm<0> = 0, op2 = 001                                                                                             |

|                 | S1E0R        | when op1 = 000, CRm<0> = 0, op2 = 010                                                                                             |

|                 | S1E0W        | when op1 = 000, CRm<0> = 0, op2 = 011                                                                                             |

|                 | S1E2R        | when op1 = 100, CRm<0> = 0, op2 = 000                                                                                             |

|                 | S1E2W        | when op1 = 100, CRm<0> = 0, op2 = 001                                                                                             |

|                 | S12E1R       | when op1 = 100, CRm<0> = 0, op2 = 100                                                                                             |

|                 | S12E1W       | when op1 = 100, CRm<0> = 0, op2 = 101                                                                                             |

|                 | S12E0R       | when op1 = 100, CRm<0> = 0, op2 = 110                                                                                             |

|                 | S12E0W       | when op1 = 100, CRm<0> = 0, op2 = 111                                                                                             |

|                 | S1E3R        | when op1 = 110, CRm<0> = 0, op2 = 000                                                                                             |

|                 | S1E3W        | when op1 = 110, CRm<0> = 0, op2 = 001                                                                                             |

|                 | When FEA     | AT_PAN2 is implemented, the following values are also valid:                                                                      |

|                 | S1E1RP       | when op1 = 000, CRm<0> = 1, op2 = 000                                                                                             |

|                 | S1E1WP       | when op1 = 000, CRm<0> = 1, op2 = 001                                                                                             |

|                 | When FEA     | AT_ATS1A is implemented, the following values are also valid:                                                                     |

|                 | S1E1A        | when op1 = 000, CRm<0> = 1, op2 = 010                                                                                             |

|                 | S1E2A        | when op1 = 100, CRm<0> = 1, op2 = 010                                                                                             |

|                 | S1E3A        | when op1 = 110, CRm<0> = 1, op2 = 010                                                                                             |

| <op1></op1>     | Is a 3-bit ı | insigned immediate, in the range 0 to 7, encoded in the "op1" field.                                                              |

- <Cm> Is a name 'Cm', with 'm' in the range 0 to 15, encoded in the "CRm" field.

- <op2> Is a 3-bit unsigned immediate, in the range 0 to 7, encoded in the "op2" field.

- <Xt> Is the 64-bit name of the general-purpose source register, encoded in the "Rt" field.

# Operation

The description of SYS gives the operational pseudocode for this instruction.

# C6.2.21 AUTDA, AUTDZA

Authenticate Data address, using key A. This instruction authenticates a data address, using a modifier and key A.

The address is in the general-purpose register that is specified by <Xd>.

The modifier is:

- In the general-purpose register or stack pointer that is specified by <Xn|SP>, for AUTDA.

- The value zero, for AUTDZA.

If the authentication passes, the upper bits of the address are restored to enable subsequent use of the address. For information on behavior if the authentication fails, see *Faulting on pointer authentication*.

### Integer

(FEAT\_PAuth)

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 5 | 4 |    | 0 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|----|---|